## alternative

The 2700B can bring to your system the clarity & definition you have been looking for. Wayward sounds (booming bass, missing highs, blaring horns, or stifled solos) are all put in their place with the SAE 2700B Half-Octave Equalizer. The flexibility of 20 controls per channel only begins to tell the story. Some facts:

- \* 0.02% THD & IM

- \* -100dB S/N Ratio

- \* Can drive any system

- \* FREE 5 YEAR Service Contract

PLUS, long-throw oil-damped slide pots for better accuracy, precision wound toroid inductors for low distortion & a pink noise generator for system balance, Built with SAE quality, the 2700B is value packed with the capability and performance you need to control your system.

PRICE: \$550.00 (suggested list)

| <u> </u>                                                                |

|-------------------------------------------------------------------------|

| Scientific Audio Electronics, Inc.                                      |

| P.O. Box 60271, Terminal Annex<br>Los Angeles, Calif. 90060             |

| Please send me more information on the SAE 27008 Half-Octave Equalizer. |

| ADDRESSSTATEZIP                                                         |

|                                                                         |

## UNIVERSAL INTERFACE BETWEEN LOW-POWER LOGIC AND LOAD DRIVERS

**BY VERN GREGORY**

PROBLEM that confronts the designer of MOS logic circuits is coupling these low-power devices to heavy loads. The job need not be too complicated, however, since there is a relatively simple circuit that can be used easily. It consists primarily of a conventional junction FET (JFET).

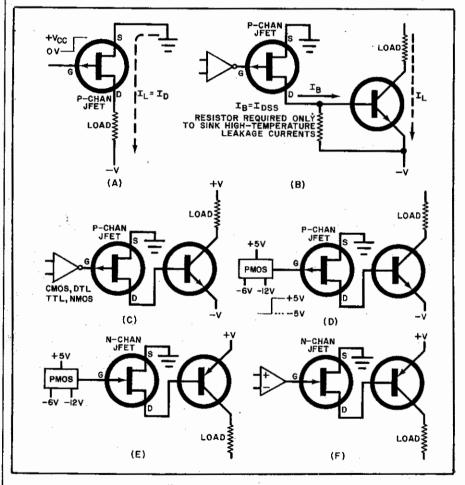

The basic circuit is shown at (A). The p-channel JFET is a normally conducting, depletion-mode device. That is, it conducts a fixed current ( $I_{\rm DSS}$ ) with

transistor, without a current-limiting resistor, as shown at (B). Here, the interfaced voltage can be at any level within the ratings of the JFET and the bipolar transistor. The base current is selected to be about 1/15 of the required load current, by choosing the proper JFET. The load current is in phase with the input to the inverter driving the JFET. Since the JFET draws no gate current, the logic element is not loaded.

zero gate voltage. When the gate voltage is increased toward positive  $V_{\rm CC}$ ,  $I_{\rm D}$  drops until pinch-off is reached. Then the current is zero.

The important feature is the fixed current at zero gate voltage. This means that the current is limited and can be selected to drive the base of a

Circuit (C) shows how to connect a 5-volt logic element (inverter shown) to a load, while (D) is a way to connect PMOS logic to a load on the negative supply. Circuit (E) is the same thing for a positive supply. The circuit at (F) illustrates an op amp or comparator interface.